What is Microcontroller?

Ans :

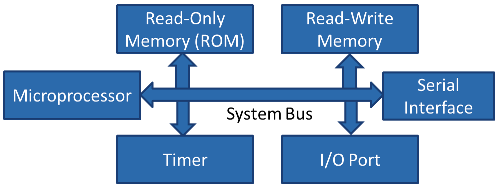

What is microcontroller is an entire computer manufactured on a single chip.

Microcontrollers are usually dedicated devices embedded within an application . For example Microcontrollers are

used as engine controllers in automobiles and as exposure and focus controllers

in cameras. In order to serve these applications, they have a high concentration

of on-chip facilities such as serial ports,parallel input output ports, timers,

counters, interrupt control,analog-to-digital converters,random access memory

,read only memory ,etc.

Difference between Microprocessor and Microcontroller

| Microprocessor | Micro Controller |

|  |

| Microprocessor is heart of Computer system. | Micro Controller is a heart of embedded system. |

| It is just a processor. Memory and I/O components have to be connected externally | Micro controller has external processor along with internal memory and i/O components |

| Since memory and I/O has to be connected externally, the circuit becomes large. | Since memory and I/O are present internally, the circuit is small. |

| Cannot be used in compact systems and hence inefficient | Can be used in compact systems and hence it is an efficient technique |

| Cost of the entire system increases | Cost of the entire system is low |

| Due to external components, the entire power consumption is high. Hence it is not suitable to used with devices running on stored power like batteries. | Since external components are low, total power consumption is less and can be used with devices running on stored power like batteries. |

| Most of the microprocessors do not have power saving features. | Most of the micro controllers have power saving modes like idle mode and power saving mode. This helps to reduce power consumption even further. |

| Since memory and I/O components are all external, each instruction will need external operation, hence it is relatively slower. | Since components are internal, most of the operations are internal instruction, hence speed is fast. |

| Microprocessor have less number of registers, hence more operations are memory based. | Micro controller have more number of registers, hence the programs are easier to write. |

| Microprocessors are based on von Neumann model/architecture where program and data are stored in same memory module | Micro controllers are based on Harvard architecture where program memory and Data memory are separate |

| Mainly used in personal computers | Used mainly in washing machine, MP3 players |

Features of 8051:

The Intel 8051 is an 8-bit microcontroller which means that most

available operations are limited to 8 bits. There are 3 basic "sizes"

of the 8051: Short, Standard, and Extended. The Short and Standard chips are

often available in DIP (dual in-line package) form, but the Extended 8051

models often have a different form factor, and are not "drop-in

compatible". All these things are called 8051 because they can all be

programmed using 8051 assembly language, and they all share certain features

(although the different models all have their own special features).

Some of the features that have made the 8051 popular are:

·

4 KB on chip program

memory.

·

128 bytes on chip data

memory(RAM)

[ 32 bank reg + 16 bit addressable reg + 80 general purpose reg

]

·

4 reg banks.

·

128 user defined

software flags.

·

8-bit data bus

·

16-bit address bus

·

16 bit timers (usually

2, but may have more, or less).

·

3 internal and 2

external interrupts.

·

Bit as well as byte

addressable RAM area of 16 bytes.

·

Four 8-bit ports,

(short models have two 8-bit ports).

·

16-bit program counter

and data pointer.

·

1 Microsecond

instruction cycle with 12 MHz Crystal.

=========================================================================================================================================

8051 addressing mode ?“. A simple question always has a simple answer too. Addressing mode is a way to address an operand. Operand means the data we are operating upon (in most cases source data). It can be a direct address of memory, it can be register names, it can be any numerical data etc. I will explain this with a simple data move instruction of 8051.

MOV A,#6AH

Here the data 6A is the operand, often known as source data. When this instruction is executed, the data 6AH is moved to accumulator A. There are 5 different ways to execute this instruction and hence we say, we have got 5 addressing modes for 8051. They are 1) Immediate addressing mode 2)Direct addressing mode 3) Register direct addressing mode 4) Register indirect addressing mode 5)Indexed addressing mode.

Immediate Addressing Mode

Let’s begin with an example.

MOV A, #6AH

In general we can write MOV A, #data

This addressing mode is named as “immediate” because it transfers an 8-bit data immediately to the accumulator (destination operand).

The picture above describes the above instruction and its execution. The opcode for MOV A, # data is 74H. The opcode is saved in program memory at 0202 address. The data 6AH is saved in program memory 0203. (See, any part of the program memory can be used, this is just an example) When the opcode 74H is read, the next step taken would be to transfer whatever data at the next program memory address (here at 0203) to accumulator A (E0H is the address of accumulator). This instruction is of two bytes and is executed in one cycle. So after the execution of this instruction, program counter will add 2 and move to o204 of program memory.

Note: The ‘#’ symbol before 6AH indicates that operand is a data (8 bit). If ‘#’ is not present then the hexadecimal number would be taken as address.

Direct Addressing Mode

This is another way of addressing an operand. Here the address of the data (source data ) is given as operand. Lets take an example.

MOV A, 04H

Here 04H is the address of register 4 of register bank#0. When this instruction is executed, what ever data is stored in register 04H is moved to accumulator. In the picture below we can see, register 04H holds the data 1FH. So the data 1FH is moved to accumulator.

Note: We have not used ‘#’ in direct addressing mode, unlike immediate mode. If we had used ‘#’, the data value 04H would have been transferred to accumulator instead 0f 1FH.

As shown in picture above this is a 2 byte instruction which requires 1 cycle to complete. Program counter will increment by 2 and stand in 0204. The opcode for instruction MOV A, address is E5H. When the instruction at 0202 is executed (E5H), accumulator is made active and ready to receive data. Then program control goes to next address that is 0203 and look up the address of the location (04H) where the source data (to be transferred to accumulator) is located. At 04H the control finds the data 1F and transfers it to accumulator and hence the execution is completed.

Register Direct Addressing Mode

In this addressing mode we use the register name directly (as source operand). An example is shown below.

MOV A, R4

At a time registers can take value from R0,R1…to R7. You may already know there are 32 such registers. So how you access 32 registers with just 8 variables to address registers? Here comes the use of register banks. There are 4 register banks named 0,1,2 and 3. Each bank has 8 registers named from R0 to R7. At a time only one register bank can be selected. Selection of register bank is made possible through a Special Function Register (SFR) named Processor Status Word (PSW). PSW is an 8 bit SFR where each bit can be programmed. Bits are designated from PSW.0 to PSW.7 Register banks are selected using PSW.3 and PSW.4 These two bits are known as register bank select bits as they are used to select register banks. A picture below shows the PSW register and the Register Bank Select bits with status.

So in register direct addressing mode, data is transferred to accumulator from the register (based on which register bank is selected).

Take a look at the picture below.

So we see that opcode for MOV A, R4 is EC. The opcode is stored in program memory address 0202 and when it is executed the control goes directly to R4 of the respected register bank (that is selected in PSW). If register bank #0 is selected then the data from R4 of register bank #0 will be moved to accumulator. (Here it is 2F stored at 04 H). 04 H is the address of R4 of register bank #0. Movement of data (2F) in this case is shown as bold line. Now please take a look at the dotted line. Here 2F is getting transferred to accumulator from data memory location 0C H. Now understand that 0C H is the address location of Register 4 (R4) of register bank #1. Programmers usually get confused with register bank selection. Also keep in mind that data at R4 of register bank #0 and register bank #1 (or even other banks) will not be same. So wrong selection of register banks will result in undesired output.

Also note that the instruction above is 1 byte and requires 1 cycle for complete execution. This means using register direct addressing mode can save program memory.

Register Indirect Addressing Mode

So in this addressing mode, address of the data (source data to transfer) is given in the register operand.

MOV A, @R0

Here the value inside R0 is considered as an address, which holds the data to be transferred to accumulator.

Example: If R0 holds the value 20H, and we have a data 2F H stored at the address 20H, then the value 2FH will get transferred to accumulator after executing this instruction. Got it? See the picture below.

So the opcode for MOV A, @R0 is E6H. Assuming that register bank #0 is selected. So the R0 of register bank #0 holds the data 20H. Program control moves to 20H where it locates the data 2FH and it transfers 2FH to accumulator.

This is a single byte instruction and the program counter increments 1 and moves to 0203 of program memory.

Note: Only R0 and R1 are allowed to form a register indirect addressing instruction. In other words programmer can must make any instruction either using @R0 or @R1. All register banks are allowed.

Indexed Addressing Mode

Well lets see two examples first.

MOVC A, @A+DPTR and MOVC A, @A+PC

where DPTR is data pointer and PC is program counter (both are 16 bit registers). Lets take the first example.

MOVC A, @A+DPTR

What’s the first impression you have now? The source operand is @A+DPTR and we know we will get the source data (to transfer) from this location. It is nothing but adding contents of DPTR with present content of accumulator. This addition will result a new data which is taken as the address of source data (to transfer). The data at this address is then transferred to accumulator. Take a look at the picture below.

The opcode for the instruction is 93H. DPTR holds the value 01FE, where 01 is located in DPH (higher 8 bits) and FE is located in DPL (lower 8 bits). Accumulator now has the value 02H. A 16 bit addition is performed and now 01FE H+02 H results in 0200 H. What ever data is in 0200 H will get transferred to accumulator. The previous value inside accumulator (02H) will get replaced with new data from 0200H. New data in the accumulator is shown in dotted line box.

This is a 1 byte instruction with 2 cycles needed for execution. What you infer from that? The execution time required for this instruction is high compared to previous instructions (which all were 1 cycle).

==================================================================================================================================================================

==================================================================================================================================================================

Port 0(p0.0 to p0.7):

It is 8-bit bi-directional I/O port. It is bit/ byte addressable. During external memory access, it functions as multiplexed data and low-order address bus AD0-AD7.

Port 1 (p1.0 to p1.7):

It is 8-bit bi-directional I/O port. It is bit/ byte addressable. When logic '1' is written into port latch then it works as input mode. It functions as simply I/O port and it does not have any alternative function.

Port 2 (p2.0 to p2.7):

It is 8-bit bi-directional I/O port. It is bit/ byte addressable. During external memory access it functions as higher order address bus (A8-A15).

Port 3(p3.0 to port 3.7):

It is 8-bit I/O port. In an alternating function each pins can be used as a special function I/O pin.

P3.0-RxD:

It is an Input signal. Through this I/P signal microcontroller receives serial data of serial communication circuit.

P3.1-TxD:

It is O/P signal of serial port. Through this signal data is transmitted.

P3.2- (INT0):

It is external hardware interrupt I/P signal. Through this user, programmer or peripheral interrupts to microcontroller.

P3.3-(INT1):

It is external hardware interrupt I/P signal. Through this user, programmer or peripheral interrupts to microcontroller.

P3.4- T0:

It is I/P signal to internal timer-0 circuit. External clock pulses can connects to timer-0 through this I/P signal.

P3.5-T1:

It is I/P signal to internal timer-1 circuit. External clock pulses can connects to timer-1 through this I/P signal.

P3.6-[WR(bar)]:

It is active low write O/P control signal. During External RAM (Data memory) access it is generated by microcontroller. when [WR(bar)]=0, then performs write operation.

P3.7-[RD(bar)]:

It is active low read O/P control signal. During External RAM (Data memory) access it is generated by microcontroller. when [RD(bar)]=0, then performs read operation from external RAM.

XTAL1 and XTAL2:

These are two I/P line for on-chip oscillator and clock generator circuit. A resonant network as quartz crystal is connected between these two pin. 8051 microcontroller also drives from external clock, then XTAL2 is used to drive 8051 from external clock and XTAL1 should be grounded.

[EA(bar)]/VPP:

It is and active low I/P to 8051 microcontroller. when (EA)= 0, then 8051 microcontroller access from external program memory (ROM) only. When (EA) = 1, then it access internal and external program memories (ROMS).

[PSEN(bar)]:

It is active low O/P signal. It is used to enable external program memory (ROM). When [PSEN(bar)]= 0, then external program memory becomes enabled and microcontroller read content of external memory location. Therefore it is connected to (OE) of external ROM. It is activated twice every external ROM memory cycle.

ALE:

Address latch enable: It is active high O/P signal. When it goes high, external address latch becomes enabling and lower address of external memory (RAM or ROM) latched into it. Thus it separates A0-A7 address from AD0-AD7. It provides properly timed signal to latch lower byte address. The ALE is activated twice in every machine cycle. If external RAM & ROM is not accessed, then ALE is activated at constant rate of 1/6 oscillator frequency, which can be used as a clock pulses for driving external devices.

RESET:

It is active high I/P signal. It should be maintained high for at least two machine cycle while oscillator is running then 8051 microcontroller resets.

==================================================================================================================================================================

(1)Write a Program to add 2 -8bit number data in stored in Register R0,R1 and result to be stored in R2.

ans:

MOV A , R0 ; LOAD THE CONTENT OF THE REGISTER R0 IN REGISTER A.

ADD A , R1 ; ADD THE CONTENT OF REGISTER A WITH THE CONTENT OF REGISTER R1.

MOV R2 , A ; STOR THE RESULT OF ADDITION IN REGISTER R2.

SJMP Here ; Stop.

(2)write a program to add 2-8bit number data is stored in internal memory and store the result in register R2:

ans:

MOV A , #44H ; LOAD THE CONTENT 44H IN REGISTER A

ADD A , #66H ; ADD THE CONTENT OF REGISTER A WITH THE CONTENT 66H.

MOV R2,, A ;STORE THE RESULT OF ADDITION IN REGISTER R2

SJMP Here ; Stop

(3)write a program to add 2 -8 bit number data is stored in data Memory location 51H ,52H AND STORE THE RESULT IN DATA MEMORY LOCATION 53H.

MOV A,51H ; LOAD REGISTER A WITH THE CONTENT OF MEMORY LOCATION 51H

ADD A, 52H ; ADD THE CONTENT OF REGISTER A WITH CONTENT OF MEMORY 52H

MOV 53H, A : SOTRE THE RESULT OF ADDITION IN DATA MEMORY 53H.

SJMP Here ; Stop.

(4)write program to add 2-8bit number Data is stored in data memory location whose address stored in R1 and R2 register and store the result in data memory location 53H.

MOV A, @R1 ;LOAD REGISTER A WITH THE CONTENT OF MEMORY LOCATION POINTER BY REGISTER R1

ADD A,@R2 ; ADD THE CONTENT OF REGISTER A WITH THE CONTENT OF LOCATION POINTER BY REGISTER R2S.

MOVE 53H, A ; STORE THE RESULT OF ADDITION IN DATA MEMORY 53H.

SJMP Here ; Stop